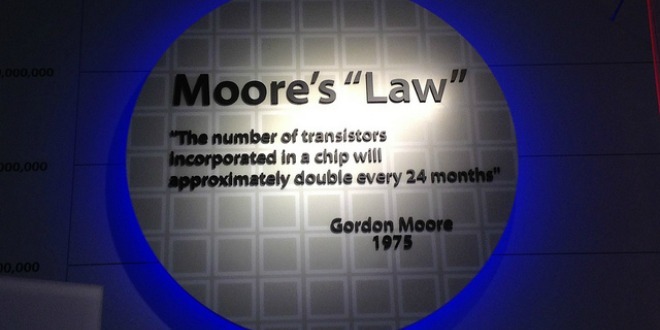

英文原文:As Moore’s Law slows, better design engineering will win out

本文原文发布在 venturebeat 上。作者 Henry Samueli 是 Broadcom(博通)联合创始人兼 CTO。Broadcom 是全球领先的有线和无线通信半导体生产公司。

在过去的 50 年,摩尔定律可靠地描述了硅芯片速度、功率和功能性的指数式增长。然而,随着历史上第一次出现每个晶体管成本的上升,我们已经进入到了一个回报递减的时代。

我们只有在硬件和软件创新上更聪明,才能从新兴的物联网中获取最大的价值。或许聪明方式是对已经进行了半个世纪的竞速按下“暂停”键,并在一个硅片上塞入更多的晶体管。

如果要实现将数百亿个设备连入互联网的愿景(思科公司预测 400 亿个智能设备和另外 100 亿个嵌入智能模块的传统机器设备),我们将需要大量低成本的、具备通信能力的芯片供给。好消息是创新和增长会以同样的速度持续发展,但是需要我们从每两年晶体管数量翻一倍的这种持续重压中暂缓一下。

至今,我们一直通过减小芯片尺寸或节点到更小纳米级别的维度,以此来保持与摩尔定律一致的发展速度。成本效益比率在 28 纳米的时候达到了最小值,而在那之后的每一个进展都需要更大的投资,因此降低了总性价比。

上图:自摩尔阐述他的观察后,单个晶体管成本第一次出现上升。随着 28 纳米的“甜蜜点”的到来,是时候去为下一代的创新而探索其他补充摩尔定律的方法了。

当然,芯片会继续缩小。我们会与其他的半导体公司继续推进到 10 纳米的目标,但是超越 10 纳米则需要发展新的科技、技术和不断完善的制造加工工艺。极紫外线(EUV)光刻、其他半导体材料、多重 3D 芯片堆栈和 450 毫米晶片只是一些新的极其昂贵的研究手段而已。

但是,我们有很多种方式利用 28 纳米来推进工业的发展,让数以千计的开发者来实现物联网的创新与增长。我们能通过设计工程而非工艺工程来推动成本、尺寸和功耗效率的进步。物联网设备通常拥有较少的晶体管数量,因此并不需要最先进的(同时也是最贵的)的过程节点。

如果以 20 纳米为最佳节点尺寸作为前提,那么坚定这个节点为选择的平台和融入更多的功能,例如模拟和射频组件,则是符合逻辑的下一步。模拟组件不像数字组件那样会缩小,但是将他们融入相对成熟的 20 纳米平台将加速万物互联,无论是小到手表、个人健康和家庭设备,还是大到汽车、运输、农业、制造业以及工业控制。

我们这类行业可以接触到低成本硬件,包括从传感器到信号转换器和无线接口。在这个行业中,我们所有人现在需要做的是将接口标准化,以确保互通性。尽管摩尔定律暂停了,但半导体的最好时代仍在前方。