class="MsoNormal" style="text-align: center;" align="center">u-boot分析(六)

上篇博文我们按照210的启动流程,分析到了关闭看门狗,今天我们继续按照u-boot的启动流程进行分析,今天我们会主要分析时钟的初始化。

今天我们会用到的文档:

1. Arm9内核手册:http://download.csdn.net/detail/wrjvszq/8358867

2. Arm11内核手册:http://download.csdn.net/detail/wrjvszq/8358877

3. Arm a8内核手册:http://download.csdn.net/detail/wrjvszq/8358893

4. 2440芯片手册:http://download.csdn.net/detail/wrjvszq/8358949

5. 6410芯片手册:http://download.csdn.net/detail/wrjvszq/8358965

6. 210芯片手册:S5PV210_UM_REV1.1(我的不知道为什么传不上去大家去百度搜吧)

由于arm的时钟体系比较复杂我们今天会通过以下几点,对arm的时钟体系进行介绍:

1. 概念解析

2. 体系介绍

3. 编程分析

l 概念解析

1. 时钟脉冲信号

由特定的电压幅度以及特定的时间间隔产生的脉冲信号

2. 时钟频率

单位时间内产生的脉冲个数

3. 时钟脉冲信号来源

时钟信号的来源有一下两种方式:

1) 晶振(晶体振荡器):石英晶体经过打磨,加电极,通电,会产生特定的时钟频率,但是高频的价格比较昂贵。

2) PLL(锁相环):需要一个外部晶振,和一个能对晶体的特定频率加倍或分频的集成锁相环电路,可以产生不同频率的时钟信号,可以得到高频信号,成本低

l 体系介绍

对于时钟体系的介绍我们将会通过下面4点来介绍:

1) 晶振频率

2) PLL个数及分类

3) 每个PLL可以产生哪些时钟

4) 时钟用于哪些外设

1. 2440时钟体系:

1) 晶振频率:12 MHZ

2) PLL个数及分类:

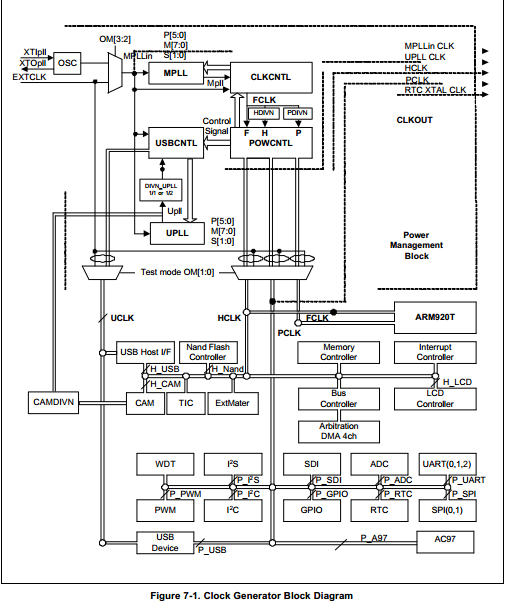

我们可以从芯片手册中的7. Clock&Power Management找到下图

从上图我们可以知道其共有两个PLL分别为MPLL和UPLL

3) PLL产生的时钟

同样是从上图我们可以看出

l MPLL产生了HCLK、PCLK、FCLK

l UPLL产生了UCLK。

4) 时钟的用途

可以总结为下表

时钟

应用场合

FCLK

Arm9

HCLK

AHB总线

LCD、DMA等

PCLK

APB总线

UART、GPIO等

UCLK

USB总线

USB设备

2. 6410时钟体系

1) 晶振频率:24MHZ

2) PLL个数及分类:

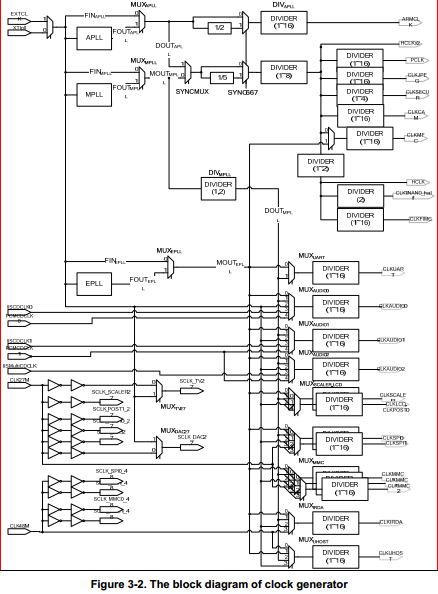

同样我们可以找到下图

从上图我们可以知道其共有三个PLL分别为MPLL、APLL和EPLL

3) PLL产生的时钟

同样是从上图我们可以看出

l MPLL产生了HCLK、PCLK

l APLL产生了ARMCLK

l EPLL产生了SCLK

4) 时钟的用途

可以总结为下表

时钟

应用场合

设备

ARMCLK

处理器

Arm11

HCLK

AHB总线

LCD、DMA等

PCLK

APB总线

UART、GPIO等

SCLK

USB总线

USB设备

3. 210时钟体系

1) 晶振频率:24MHZ

2) PLL个数及分类:

同样我们可以找到下图

从上图我们可以知道其共有三个PLL分别为MPLL、APLL、EPLL和VPLL

3) PLL产生的时钟

同样是从上图我们可以看出

l APLL产生了MSYS体系的时钟包括ARMCLK、HCLK_MSYS、PCLK_MSYS

l MPLL产生了DSYS体系的时钟HCLK_DSYS、PCLK_DSYS

l EPLL产生了PSYS体系的时钟HCLK_PSYS、PCLK_PSYS

l VPLL产生视频相关时钟

4) 时钟的用途

可以总结为下表

经过上述内容我们对arm时钟体系有了一定的了解,接下来我们分析其编程方法。

l 编程分析

1. 初始化流程

通过阅读210的芯片手册,很轻松我们在3.5 CLOCK CONFIGURATION PROCEDURE可以找到其配置过程

2. 如何配置

我们将上面找到的基本的配置流程,和u-boot的代码比较一下,发现其步骤是一样的,大部分的设置比较简单(参照文档的说明即可),在此我就不一一分析了。

1 system_clock_init: 2 3 ldr r0, =ELFIN_CLOCK_POWER_BASE @0xe0100000 4 5 /* Set Mux to FIN */ 6 ldr r1, =0x0 7 str r1, [r0, #CLK_SRC0_OFFSET] 8 9 ldr r1, =APLL_LOCKTIME_VAL 10 str r1, [r0, #APLL_LOCK_OFFSET] 11 12 /* Disable PLL */ 13 ldr r1, =0x0 14 str r1, [r0, #APLL_CON0_OFFSET] 15 ldr r1, =0x0 16 str r1, [r0, #MPLL_CON_OFFSET] 17 18 ldr r1, =0x0 19 str r1, [r0, #MPLL_CON_OFFSET] 20 21 ldr r1, [r0, #CLK_DIV0_OFFSET] 22 ldr r2, =CLK_DIV0_MASK 23 bic r1, r1, r2 24 25 ldr r2, =CLK_DIV0_VAL 26 orr r1, r1, r2 27 str r1, [r0, #CLK_DIV0_OFFSET] 28 29 ldr r1, =APLL_VAL 30 str r1, [r0, #APLL_CON0_OFFSET] 31 32 ldr r1, =MPLL_VAL 33 str r1, [r0, #MPLL_CON_OFFSET] 34 35 ldr r1, =VPLL_VAL 36 str r1, [r0, #VPLL_CON_OFFSET] 37 #if defined(CONFIG_EVT1) 38 ldr r1, =AFC_ON 39 str r1, [r0, #APLL_CON1_OFFSET] 40 #endif 41 mov r1, #0x10000 42 1: subs r1, r1, #1 43 bne 1b 44 45 ldr r1, [r0, #CLK_SRC0_OFFSET] 46 ldr r2, =0x10001111 47 orr r1, r1, r2 48 str r1, [r0, #CLK_SRC0_OFFSET] 49 50 #if defined(CONFIG_MCP_AC) 51 52 /* CLK_SRC6[25:24] -> OneDRAM clock sel = MPLL */ 53 ldr r1, [r0, #CLK_SRC6_OFFSET] 54 bic r1, r1, #(0x3<<24) 55 orr r1, r1, #0x01000000 56 str r1, [r0, #CLK_SRC6_OFFSET] 57 58 /* CLK_DIV6[31:28] -> 4=1/5, 3=1/4(166MHZ@667MHz), 2=1/3 */ 59 ldr r1, [r0, #CLK_DIV6_OFFSET] 60 bic r1, r1, #(0xF<<28) 61 bic r1, r1, #(0x7<<12) @; ONENAND_RATIO: 0 62 orr r1, r1, #0x30000000 63 str r1, [r0, #CLK_DIV6_OFFSET] 64 65 #elif defined (CONFIG_MCP_H) 66 67 /* CLK_SRC6[25:24] -> OneDRAM clock sel = 00:SCLKA2M, 01:SCLKMPLL */ 68 ldr r1, [r0, #CLK_SRC6_OFFSET] 69 bic r1, r1, #(0x3<<24) 70 orr r1, r1, #0x00000000 71 str r1, [r0, #CLK_SRC6_OFFSET] 72 73 /* CLK_DIV6[31:28] -> 4=1/5, 3=1/4(166MHZ@667MHz), 2=1/3 */ 74 ldr r1, [r0, #CLK_DIV6_OFFSET] 75 bic r1, r1, #(0xF<<28) 76 bic r1, r1, #(0x7<<12) @; ONENAND_RATIO: 0 77 orr r1, r1, #0x00000000 78 str r1, [r0, #CLK_DIV6_OFFSET] 79 80 #elif defined (CONFIG_MCP_B) || defined (CONFIG_MCP_D) 81 82 /* CLK_SRC6[25:24] -> OneDRAM clock sel = 00:SCLKA2M, 01:SCLKMPLL */ 83 ldr r1, [r0, #CLK_SRC6_OFFSET] 84 bic r1, r1, #(0x3<<24) 85 orr r1, r1, #0x01000000 86 str r1, [r0, #CLK_SRC6_OFFSET] 87 88 /* CLK_DIV6[31:28] -> 4=1/5, 3=1/4(166MHZ@667MHz), 2=1/3 */ 89 ldr r1, [r0, #CLK_DIV6_OFFSET] 90 bic r1, r1, #(0xF<<28) 91 bic r1, r1, #(0x7<<12) @; ONENAND_RATIO: 0 92 orr r1, r1, #0x30000000 93 str r1, [r0, #CLK_DIV6_OFFSET] 94 95 #elif defined (CONFIG_MCP_SINGLE) 96 97 /* CLK_DIV6 */ 98 ldr r1, [r0, #CLK_DIV6_OFFSET] 99 bic r1, r1, #(0x7<<12) @; ONENAND_RATIO: 0 100 str r1, [r0, #CLK_DIV6_OFFSET] 101 102 #endif 103 104 mov pc, lr